#### POWERLINK – Use Cases in open, POWERLINK compatible networks

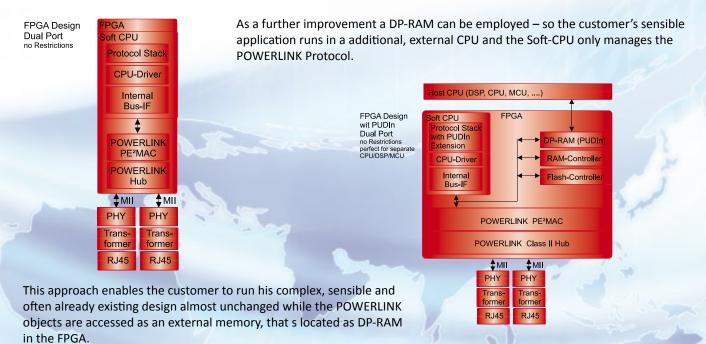

#### POWERLINK with FPGA and Soft-CPU

This case is the most common use case, it allows for an excellent POWERLINK Performance and supports all outstanding POWERLINK features.

In this scenario a Hub-IP Core ensures low latency and low jitter in the line-structure of the network.

A special component PE<sup>2</sup>MAC (POWERLINK Enhanced Ethernet MAC) provides a Autoreply functionality, which basically answers Poll-Request from the MN almost instantly with the corresponding Poll-Response. This results in an overall excellent performance and specially low jitter.

In a Soft-CPU in the same FPGA the POWERLINK Protocol is being managed and the customer's application is running.

Available Products from port: Protocol Stack (with PUDIn Support) POWERLINK CN Protocol Stack, ANSI-C Source Code Driver for MCU (NIOS or Microblaze) For POWERLINK CN Protocolo Stack, ANSI-C Source Code POWERLINK DesignTool Tool for generating fast and costeffective POWERLINK applications (Controlled Nodes). POWERLINK-Hub IP-Core POWERLINK HUB IP - Core for XILINX or Altera FPGA, VHDL Source Code. The EPL Hub is optimized for low latency. POWERLINK MAC (PE<sup>2</sup>MAC) POWERLINK Enhanced Ethernet MAC IP-Core, VHDL Source Code für Xilinx or Altera FPGAs. The MAC offers extremely fast Poll Responses operating POWERLINK.

#### ETHERNET 🔳 POWERLINK

#### **POWERLINK with FPGA and external MCU**

This use case allows to combine the advantages of high speed / low jitter connectivity of the FPGA Ethernet access solution with the performance and the perherial components of a silicon MCU.

Existing or price effective silicon MCUs with Flash/RAM and the proper peripherials on-board are often good enough for reasonable POWERLINK performance.

They add less money and components to the BOM than the external SD-RAM and serial Flash for the Soft-CPU would add. Depending on the Software-Design and the System-Load Cycle Times down to 1ms can be realised.

| Dual Port<br>no Restrictions           | MCU                     |                  |         |

|----------------------------------------|-------------------------|------------------|---------|

| FPGA with<br>9000 Gates<br>sufficient: | Protoco<br>SRAM-        | _                |         |

|                                        | On-B<br>SRAI            |                  |         |

|                                        | FPGA                    | parallel S       | SRAM-IF |

|                                        | POWE<br>PE <sup>2</sup> |                  |         |

|                                        | POWE<br>Hu              |                  |         |

|                                        | <b>‡</b> MII            | ‡mii             |         |

|                                        | PHY                     | PHY              | 0.6     |

|                                        | Trans-<br>former        | Trans-<br>former | 2       |

|                                        | RJ45                    | RJ45             |         |

Available Products from port: **Protocol Stack** POWERLINK CN Protocol Stack, ANSI-C Source Code Driver for MCU (STM32, Luminary, ...) For POWERLINK CN Protcolo Stack, ANSI-C Source Code **POWERLINK DesignTool** Tool for generating fast and costeffective POWERLINK applications (Controlled Nodes). **POWERLINK-Hub IP-Core** POWERLINK HUB IP - Core for XILINX or Altera FPGA, VHDL Source Code. The EPL Hub is optimized for low latency. POWERLINK MAC (PE<sup>2</sup>MAC) POWERLINK Enhanced Ethernet MAC IP-Core, VHDL Source Code für Xilinx or Altera FPGAs. The MAC offers extremely fast Poll Responses operating POWERLINK.

### ETHERNET **POWERLINK**

#### **POWERLINK with FPGA and external Linux-CPU**

Instead of the MCU a powerfull CPU (e.g. Arm9, i.MX) can be employed.

Normally running POWERLINK on Linux Systems would limit cycle time and possible jitter to values that are not acceptable for industrial applications.

Combining the Linux CPU with the FPGA enables the Linux CPU at least theoretical to manage all possible cycle times and low jitter. The bottleneck is now the protocol stack that would need to run completely in the Kernel Space in Kernel-Mode to comply to POWERLINK's speed requirements.

Bringing large protocol libraries into the Kernel-Mode increases risks and reduces overall stability of the Linux system. Therefore port has created a Kernel-Mode POWERLINK Kernel Mode Interface that runs in the Kernel Space while ports POWERLINK Library runs in the User-Mode.

This separation enables Linux for the industrial grade cycle times and jitter AND maintains the Linux concept of a fast Kernel-Mode Interface and a dedicated User-Mode application.

| Linux Support                          | Linux CF                                 | PU/MCU           |         |

|----------------------------------------|------------------------------------------|------------------|---------|

| Protocol Stack<br>in User Mode         | Protoco<br>User Spa                      |                  |         |

| Slim Kernel<br>Mode Interface          | SRAM<br>Kernel Sp                        |                  | 58      |

|                                        |                                          | parallel S       | SRAM-IF |

| FPGA with<br>9000 Gates<br>sufficient: | FPGA<br>POWERLINK<br>PE <sup>2</sup> MAC |                  |         |

|                                        | POWERLINK<br>Hub                         |                  | 22      |

|                                        | ‡ MII                                    | ‡mii             |         |

|                                        | PHY                                      | PHY              |         |

|                                        | Trans-<br>former                         | Trans-<br>former |         |

|                                        | RJ45                                     | RJ45             |         |

Available Products from port: Protocol Stack POWERLINK CN Protocol Stack, ANSI-C Source Code Driver for CPU (GPL Kernel Mode Interface) For POWERLINK CN Protocolo Stack, ANSI-C Source Code POWERLINK DesignTool Tool for generating fast and costeffective POWERLINK applications (Controlled Nodes). POWERLINK-Hub IP-Core POWERLINK HUB IP - Core for XILINX or Altera FPGA, VHDL Source Code. The EPL Hub is optimized for low latency. POWERLINK MAC (PE<sup>2</sup>MAC) POWERLINK Enhanced Ethernet MAC IP-Core, VHDL Source Code für Xilinx or Altera FPGAs. The MAC offers extremely fast Poll Responses operating POWERLINK.

### POWERLINK

#### **POWERLINK with Linux SoC**

A special use-case of the Linux System is the SoC (e.g. ZYNQ)

Here the FPGA and a powerful Linux CPU are combined on a single chip.

Here as well the advantages of the Kernel-Mode Interface and the User Mode operated POWERLINK protocol stack are combined. Linux becomes enabled for the industrial grade cycle times and jitter AND Linux' concept of a fast Kernel-Mode Interface and a dedicated User-Mode application is maintained.

| Linux Support                          | Linux CPU/MCU                    |             |        |  |

|----------------------------------------|----------------------------------|-------------|--------|--|

| Protocol Stack<br>in User Mode         | Protoco                          | l Stack     |        |  |

|                                        | User Spa                         | ce          |        |  |

| Slim Kernel<br>Mode Interface          | SRAM                             | -Driver     |        |  |

|                                        | Kernel Space                     |             |        |  |

|                                        | 4                                | parallel SF | RAM-IF |  |

| FPGA with<br>9000 Gates<br>sufficient: | FPGA                             |             |        |  |

|                                        | POWERLINK<br>PE <sup>2</sup> MAC |             |        |  |

|                                        | POWE<br>Hu                       |             |        |  |

|                                        | <b>‡</b> MII                     | ¢MII        |        |  |

|                                        | PHY                              | PHY         |        |  |

|                                        | Trans-                           | Trans-      |        |  |

|                                        | former                           | former      |        |  |

|                                        |                                  |             |        |  |

#### Available Products from port: Protocol Stack POWERLINK CN Protocol Stack, ANSI-C Source Code Driver for ZYNQ (GPL Kernel Mode Interface) For POWERLINK CN Protoclo Stack, ANSI-C Source Code POWERLINK DesignTool Tool for generating fast and costeffective POWERLINK applications (Controlled Nodes). POWERLINK-Hub IP-Core POWERLINK HUB IP - Core for ZYNQ, VHDL Source Code. The EPL Hub is optimized POWERLINK MAC (PE<sup>2</sup>MAC)

POWERLINK Enhanced Ethernet MAC IP-Core, VHDL Source Code für ZYNQ FPGAs. The MAC offers extremely fast Poll Responses operating POWERLINK.

### ethernet **POWERLINK**

#### POWERLINK with TI's Sitara AM335x

Port's POWERLINK Protocol Library supports POWERLINK on TI's versatile platform Sitara. The on-chip periphrials ICSS (Industrial Communication Sub System) with the parts PRU (Programmanle Real Time Units) deliver an outstanding support for the POWERLINK specific support in ()programmable) hardware. Besides POWERLINK other Ethernet based fieldbusses are supported as well. Currently TI's Real Time OS Sys/BIOS is supported, Linux Support is under construction.

|                                         | Sitara Am335x           |

|-----------------------------------------|-------------------------|

| POWERLINK<br>on TI's PRUs               | Protocol Stack          |

| - excellent<br>POWERLINK<br>Performance | Sys/BIOS<br>PRU -Driver |

| - integrated                            | \$                      |

| POWERLINK<br>periphrials                | ICSS                    |

|                                         | PRU PRU                 |

|                                         | ‡міі ‡міі               |

|                                         | PHY PHY                 |

Trans

forme RJ45 Transformer

**RJ45**

## POWERLINK

The following Use Cases are only suitable for applications with limited POWERLINK requirements. Significant limitations in Cycle Time, Jitter and Latency apply.

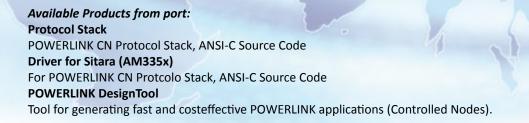

#### POWERLINK with Repeater-Mode Switch Controller and external CPU

This approach combines the price effective silicon MCUs with Flash/RAM and the proper peripherials on-board with a Silicon Switch controller for provinding line structure.

Some Switch controller manufacturer provide a feature calle Repeater Mode, which provides lowlatency and low jitter troughout the network.

This approach – providing Line Structure – comes with the lowest BOM cost, however shorther cycle times than 1ms are not possible.

#### Available Products from port: Protocol Stack POWERLINK CN Protocol Stack, ANSI-C Source Code Driver for MCU (STM32, Luminary, ...)

For POWERLINK CN Protcolo Stack, ANSI-C Source Code

POWERLINK DesignTool

Tool for generating fast and costeffective POWERLINK applications (Controlled Nodes).

PROFI

#### **POWERLINK with CPU in Star Structure**

This use case describes the lowest cost BOM approach – utilizing the start structure topology. The POWERLINK Protocol Stack is employed on the same MCU as the application is running. This makes sense for cost sensitive applications with only medium performance requirements. A cycle time down to 1ms is possible – however this depends on the software architecture.

| Single Port MCU                                                       | Available Products from port:                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Restrictions apply<br>Protocol Stack<br>MAC-Driver<br>On-board<br>MAC | Protocol Stack<br>POWERLINK CN Protocol Stack, ANSI-C Source Code<br>Driver for MCU (STM32, Luminary,)<br>For POWERLINK CN Protocolo Stack, ANSI-C Source Code<br>POWERLINK DesignTool<br>Tool for generating fast and costeffective POWERLINK applications (Controlled Nodes). |

|                                                                       |                                                                                                                                                                                                                                                                                 |

**EtherCAT**

ETHERNET

POWERLINK

EtherNet/IP

CANopea

### POWERLINK

#### POWERLINK – available components and Tools by port *Protocol Stack = Library + Driver*

The POWERLINK Protocol Stack for Controlled Nodes (CNs) by port provides POWERLINK functionality for devices.

The Protocol Stack consists from the POWERLINK Library and the POWERLINK Driver. While the Library is hardware independent, the Driver connects the Library to the specific hardware and optional to the OS.

This way the Library can be used on almost any hardware platform without "porting" it to the new hardware platform. Only the Driver needs to be created with significantly less effort. The POWERLINK Protocol Stack can be used with Operating Systems (OS) and without – running on plain hardware.

Several hardware platforms are currently supported: STR9, STM32, Luminary, Am335x, NIOS and MicroBlaze.

The Kernel-Mode Linux Driver for port's POWERLINK enables Linux POWERLINK applications for the high POWERLINK performance of the Kernel-Mode solution but maintains the integrity of the system with the Library running in User-Mode. While the MCU platforms (STM32, Luminary) are able to provide cost effective, low ressource POWERLINK connectivity, the

FPGA solutions enables Embedded Systems for the maximum POWERLINK performance.

#### Advantages/USPs

- FPGAs supported as well as MCUs and Linux Systems

- Suitable for Embedded Systems with no or any OS

- Suitable for high performance Linux applications

- o Kernel-Mode Driver

- o User-Mode Library

- New platforms easy supported

- DesignTool support

- Delivery in Source Code

#### **POWERLINK MAC (PE<sup>2</sup>MAC)**

Port's POWERLINK Enhanced Ethernet MAC (PE<sup>2</sup>MAC) is a VHDL written IP-Core for Altera and Xilinx FPGAs.

The Core of the PE<sup>2</sup>MAC is a set of Compare/Capture Registers that can trigger on the Poll-Request message, sent by the Managing Node (MN). Upon reception of the Poll-Request message the PE<sup>2</sup>MAC automatically responds "in hardware" with the preconfigured Poll-Response message. This functionaltity enables the CN for cycle times down to 200µs and for an exceptional low jitter over the complete network.

The PE<sup>2</sup>MAC operates best with port's POWERLINK Hub and port's POWERLINK Protocol Stack.

#### **POWERLINK Hub**

The POWERLINK Hub by port is a Class 2 Repeating Hub wit 3 MII-ports for use in POWERLINk networks. It only introduces below 360ns delay (including delay by the PHYs) and less than 40ns Jitter.

The POWERLINK Hub integrates seamless with the PE<sup>2</sup>MAC

Missing Driver or missing Feature

Port is available for creating new driver or missing features.

## ETHERNET **POWERLINK**

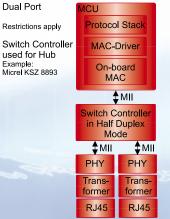

#### DesignTool

Port's POWERLINK DesignTool configures the Library, the Driver, the Objects and creates the XDD-File.

Port's POWERLINK DesignTool generates the 'fabric' to combine User-Application, Protocol-Stack and the XDD-File to be a POW-ERLINK CN-Device.

The SW-Engineer configures using this GUI-Tool port's POWERLINK Protocol Stack, creates the POWERLINK-objects and creates his own variables-definitions. Upon pressing a button the tool creates the 'fabric', consisting from various Header-Files and from the XDD-File. Further a reasonable documentation is created.

The DesignTool saves development time, reduces design cycles and improves the quality of the product creation process.

www.port.de

GERMANY

Web:

ETHERNET

POWERLINK

EtherNet/IP